Chisel(Constructing hardware in a Scala embedded language)の入門書"Digital Design with Chiselが無料で公開されているみたい。

(amazonからパーパーパックを購入することも可能。)

詳細は下記のリンクにて。

Chisel(Constructing hardware in a Scala embedded language)の入門書"Digital Design with Chiselが無料で公開されているみたい。

(amazonからパーパーパックを購入することも可能。)

詳細は下記のリンクにて。

Quartus Primeでメモリ(初期値あり)のコードをコンパイルしたら怒られた。

どうやら、初期値を設定する場合はメモリの内部構成モードを変更しないといけないみたい。

メニューバーの[Assignments] => [Device] => [Device and pin Options]を選択する。

Categoryの[Configuration]を選択し、Configuration modeを[Single Compressed Image with Memory Initialization]に設定する。

Raspberry Pi FoundationがRaspberry Pi 4を発表したみたい。

[主な仕様]

・プロセッサ:4コアARM Cortex A72(1.5GHz)(性能が先代の3倍以上)

・HDMIポート:type-Aからtype-Dの2ポートになり、60fpsの4K動画に対応。

・価格:RAMの容量により異なり、1GBが35ドル、2GBは45ドル、4GBは55ドル。

・ケース:通常は5ドル、USB Type-Cの電源は8ドル。

詳細は以下のページにて。

www.raspberrypi.org

VerilogHDLの言語仕様ではwireとして宣言されていない信号線は暗黙的に1bitのwireとして解釈される。一応、Warningとしてコンパイラが教えてくれるのだが、これが原因で何時間もデバッグする羽目になる事もある。。。

そこで、"`default_nettype wire”宣言と"`default_nettype wire"宣言を用いて、暗黙的な解釈を回避する。

記述例は以下の通りである。

`default_nettype wire module module_name(); (...回路記述...) endmodule `default_nettype wire

これで、暗黙的な解釈はされず、wireとして宣言されていない信号線はエラーとしてコンパイラが教えてくれる。

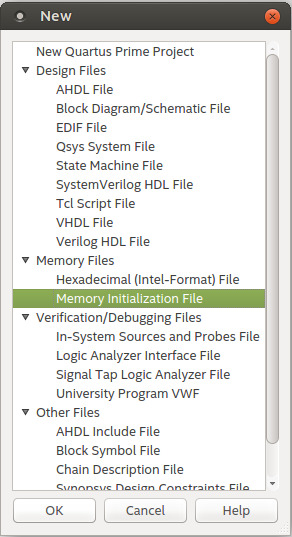

Quartus PrimeのIPcatalogから生成するメモリモジュールに初期値を設定するために、MIFを作成する。

[File] -> [New]よりMemory Initialization Fileを選択する。

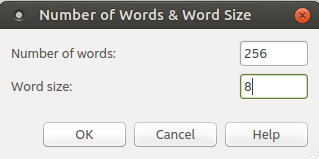

メモリのワード数とワード幅を設定する。

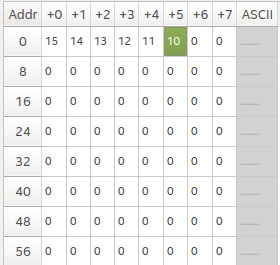

初期値を10進数で設定する。

初期値の設定が完了したら、[File] -> [Save]で作成したMIFを保存する。

複数のモジュール内で同じヘッダファイルをincludeしたSystemVerilog記述をQuartus Primeでコンパイルしたところ、競合が生じてエラーが出た。

ModelSimでの論理シミュレーション時は大丈夫だったのだが、Quartus Primeのコンパイラは厳しいようである。

と言うわけで、競合を回避するために以下の記述を各モジュールに追記し、競合を回避した。

`ifndef DEF_HEADDER

`include "def.h"

`define DEF_HEADDER

`endif

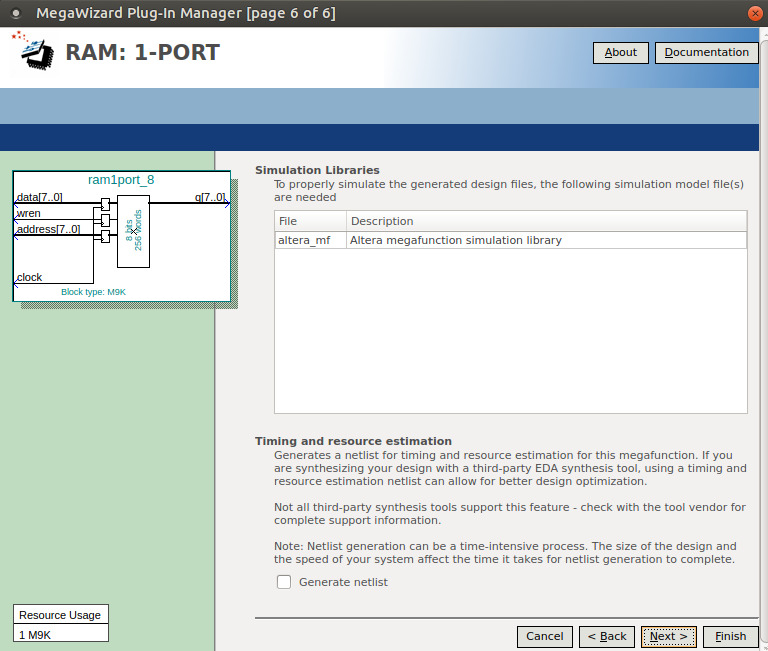

FPGA(MAX10)でそこそこの容量のメモリを使いたいのだが、レジスタで構成すると、LEをかなり消費する。というわけで、IP Catalogで用意されている、シングルポートRAM(同期書き込み、同期読み出し)を生成してみる。

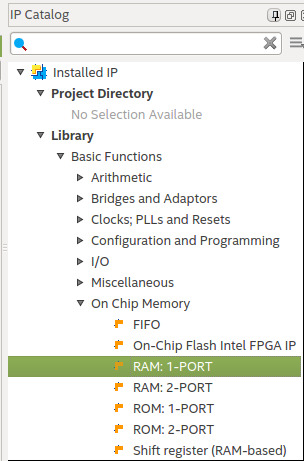

メニューバーの[Tools] -> [IP Catalog]を選択する。

[IP Catalog]の[On Chip Memory]から[RAM: 1-PORT]を選択する。

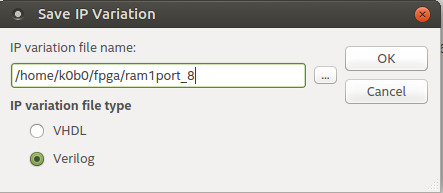

生成するシングルポートRAMの名前と保存先を入力し、MegaWizardを立ち上げる。

(ここでは、名前を[ram1port_8]とし、生成するコードはVerilogHDLとした。)

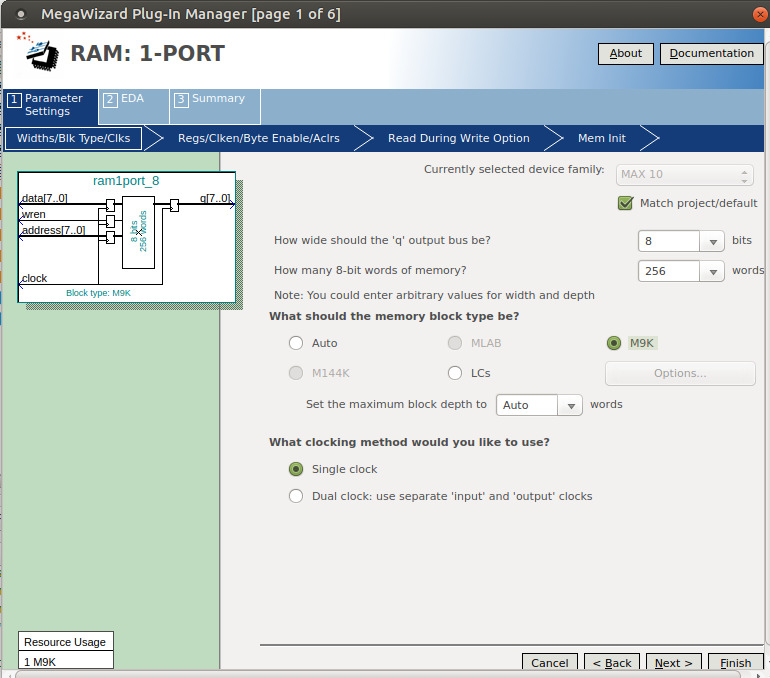

注意:MegaWizardの画面表示が小さいと操作の途中でなぜかフリーズする。立ち上げてからまず、スクロールバーが消えるくらい画面を大きくするとフリーズせずスムーズに作業を進めることができる。

データ幅、メモリ容量、メモリブロックタイプを指定する。

(ここでは、データ幅を8とし、メモリ容量を256、メモリブロックタイプをM9Kとした。)

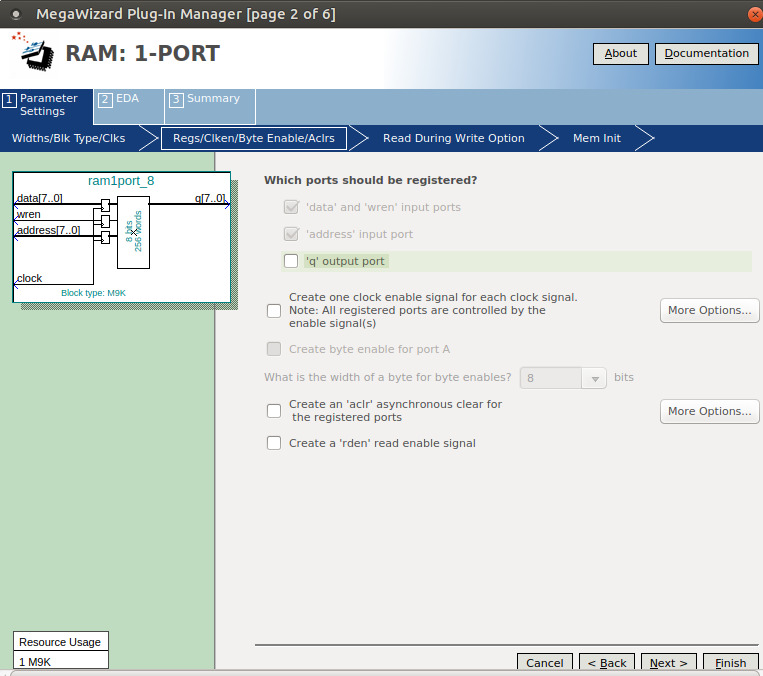

「Which ports should be registerd ?」の「'q' output port」のチェックマークを外す。

(チェックマークを外さない場合は同期書き込み・同期読み出しのシングルポートRAMを生成することとなる。)

「Single Port Write During Read Option」を「New Data」に設定する。

特に何も指定せず、「Next」を選択する。

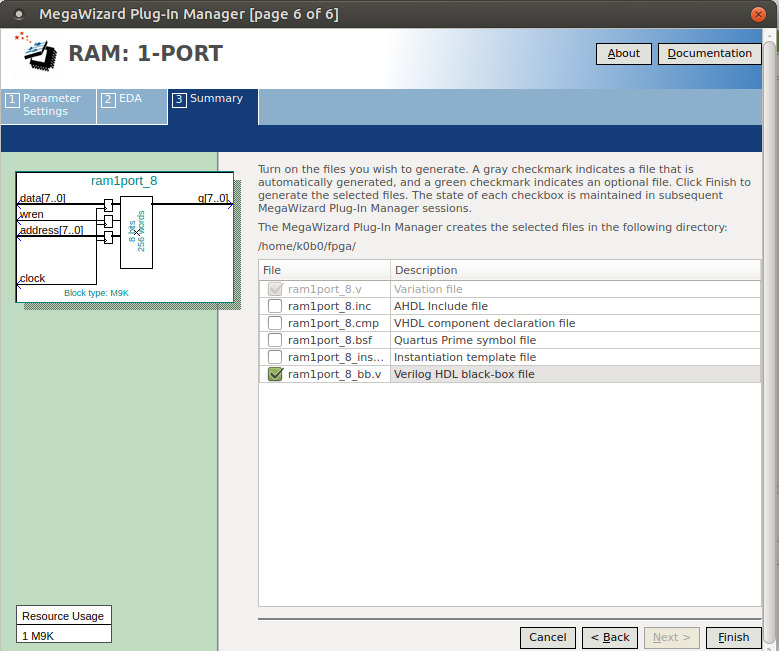

生成したいファイルにチェックマークをつけて「Finish」を選択する。

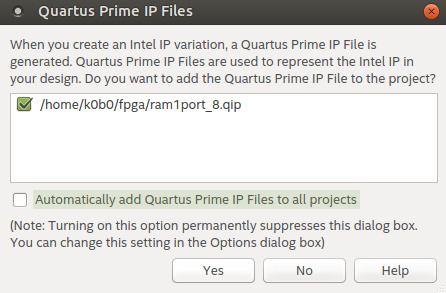

「yes」を選択する。

(これで、シングルポートRAMの生成は完了。)