Quartus Prime のIP Catalogを使ってシングルポートRAM(同期書き込み、非同期読み出し)を生成してみる。@2019/06/14 追記

IP Catalogを使ってシングルポートRAM(同期書き込み、非同期読み出し)を生成してみる。

FPGA(MAX10)でそこそこの容量のメモリを使いたいのだが、レジスタで構成すると、LEをかなり消費する。というわけで、IP Catalogで用意されている、シングルポートRAM(同期書き込み、同期読み出し)を生成してみる。

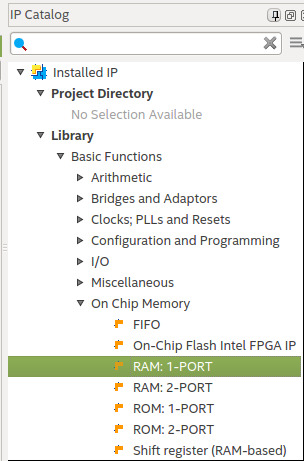

メニューバーの[Tools] -> [IP Catalog]を選択する。

[IP Catalog]の[On Chip Memory]から[RAM: 1-PORT]を選択する。

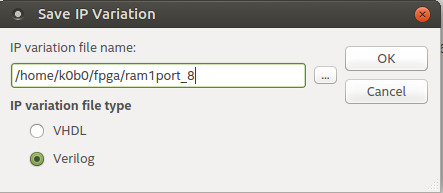

生成するシングルポートRAMの名前と保存先を入力し、MegaWizardを立ち上げる。

(ここでは、名前を[ram1port_8]とし、生成するコードはVerilogHDLとした。)

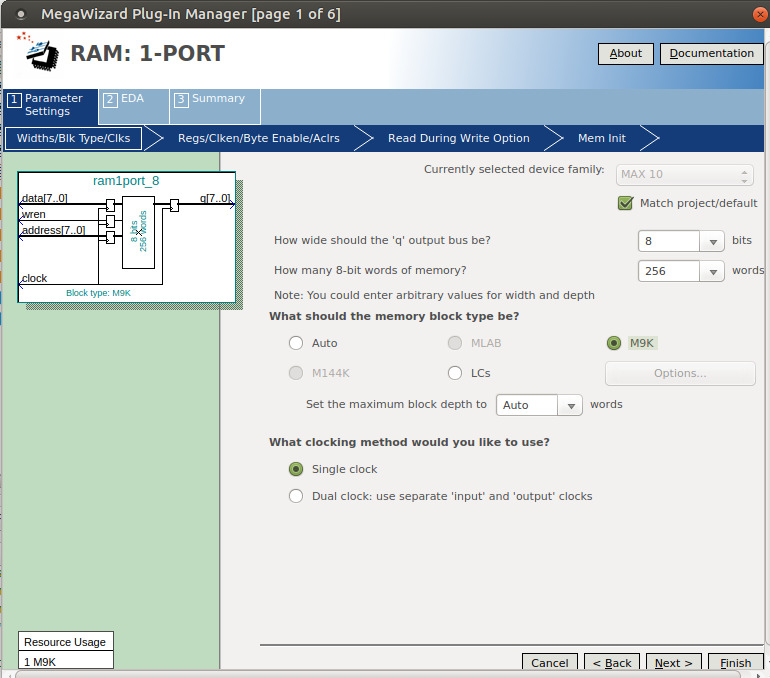

注意:MegaWizardの画面表示が小さいと操作の途中でなぜかフリーズする。立ち上げてからまず、スクロールバーが消えるくらい画面を大きくするとフリーズせずスムーズに作業を進めることができる。

データ幅、メモリ容量、メモリブロックタイプを指定する。

(ここでは、データ幅を8とし、メモリ容量を256、メモリブロックタイプをM9Kとした。)

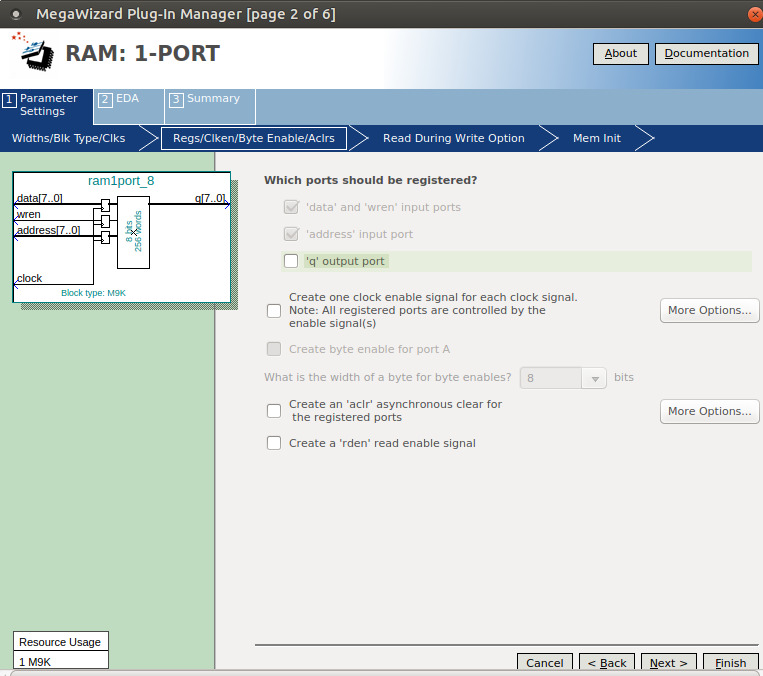

「Which ports should be registerd ?」の「'q' output port」のチェックマークを外す。

(チェックマークを外さない場合は同期書き込み・同期読み出しのシングルポートRAMを生成することとなる。)

「Single Port Write During Read Option」を「New Data」に設定する。

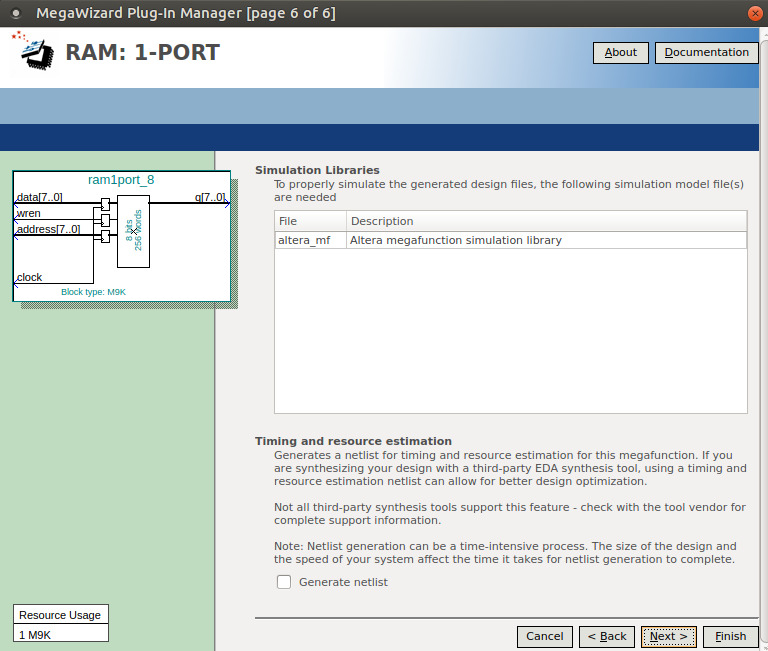

特に何も指定せず、「Next」を選択する。

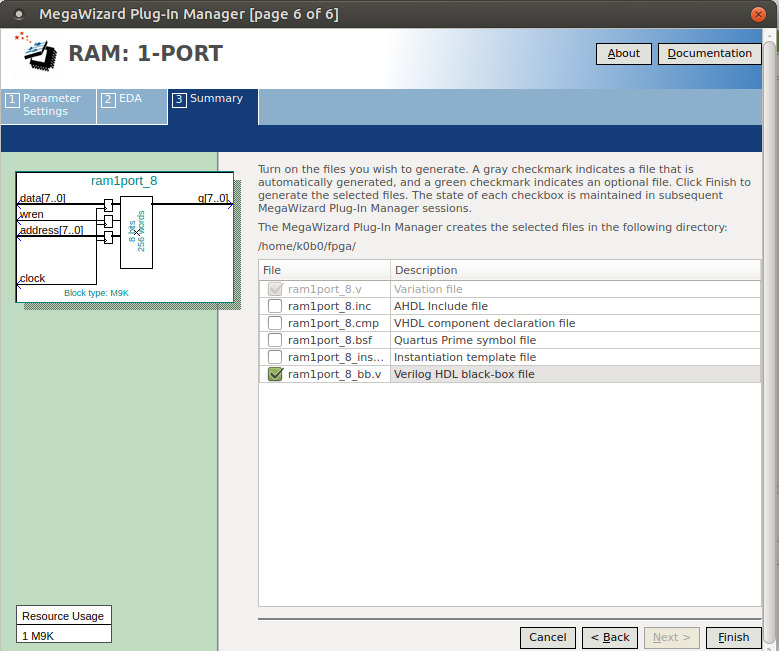

生成したいファイルにチェックマークをつけて「Finish」を選択する。

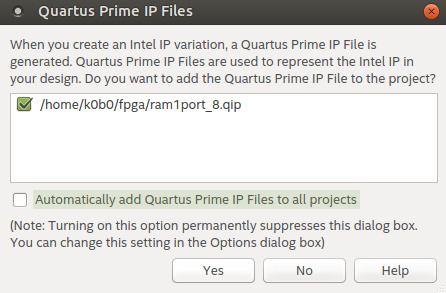

「yes」を選択する。

(これで、シングルポートRAMの生成は完了。)