RISC-V 基本命令セットRV32Iについて(2) [@20180220 update]

RISC-Vの基本命令セットRV32Iについて(2)

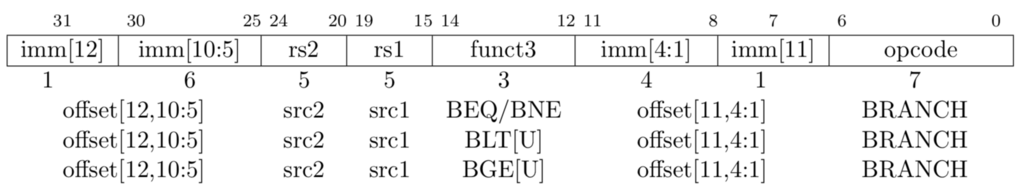

条件分岐命令(Conditional Branches)

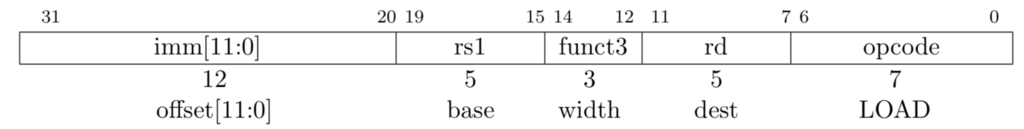

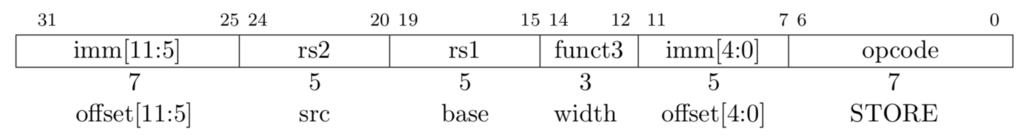

ロード/ストア命令(Load and Store Instructions)

ロード命令

ストア命令

制御およびステータスレジスタ命令(CSR:Control and Status Register Instructions)

CSR Instructions

備考

近日中に追記予定。

参考

Specifications - RISC-V Foundation