RISC-V 命令セットアーキテクチャ(ISA)の構成とレジスタファイルの構成

RISC-Vの特直(改めて)

- 単純な命令セット

- 条件フラグの削除

- 加減算のオーバーフローを無視

- 16ビット可変長な命令エンコーディング

- 分岐遅延スロットの削除

- 乗除算のためのHI/LOレジスタの削除

- リトルエンディアン方式

命令セットアーキテクチャ(ISA)の構成

RISC-VにおけるISAの構成の記法

RISC-Vではレジスタ長やビット幅、数ある命令のどれを実装しているかを表すために以下の記法でそのISAの構成を記述する。

RV + レジスタ長 + 実装命令種別

RISC-Vの基本的なISAの構成

RISC-Vの基本的なISAの構成を以下に示す。RISC-Vで推奨されるISAの構成はRV32IMAFD(RV32G(G:General))またはRV64MAFD(RV64G)である。

RV32I or RV64I or RV128I + 拡張命令

RISC-Vの基本命令

| 命令セットアーキテクチャ | 内容 |

|---|---|

| RV32I | 32ビット・アーキテクチャ(整数命令) 32ビット汎用レジスタ×32本 |

| RV32E | 32ビット・アーキテクチャ(整数命令)32ビット汎用レジスタ×16本 |

| RV64I | 64ビット・アーキテクチャ(整数命令)64ビット汎用レジスタ×32本 |

| RV128I | 128ビット・アーキテクチャ(整数命令)128ビット汎用レジスタ×32本 |

RISC-Vの拡張命令

| 命令セットアーキテクチャ | 内容 |

|---|---|

| M (Multiplication and Division) | 整数乗算命令・整数除算命令 |

| A (Atomic Instructions) | アトミックアクセス命令(メモリアクセス時に他のバス・マスタのアクセスを許可しない) |

| F (Single-Precision Floating-Point) | 単精度浮動小数点演算命令(32ビット) |

| D (Double-Precision Floating-Point) | 倍精度浮動小数点演算命令(64ビット) |

| Q (Quad-Precision Floating-Point) | 4倍精度浮動小数点演算命令(128ビット) |

| L (Decimal Floating-Point) | 10進浮動小数点演算命令(128ビット) |

| C (Compressed Instructions) | 短縮命令(16ビット長命令) |

| B (Bit Manipulation) | ビット操作命令 |

| J (Dynamically Translated Languages) | 動的言語対応命令(java、javascript等の動的チェックやガーべジ・コレクション) |

| T (Transactional Memory) | ソフトウェア・トランザクショナルメモリ対応命令(並列計算の共有メモリアクセス) |

| P (Packed-SIMD Instructions) | パックド形式SIMD命令 |

| V (Vector Operations) | ベクタ演算命令 |

| N (User-Level Interrupts) | ユーザ・レベル割り込み対応命令 |

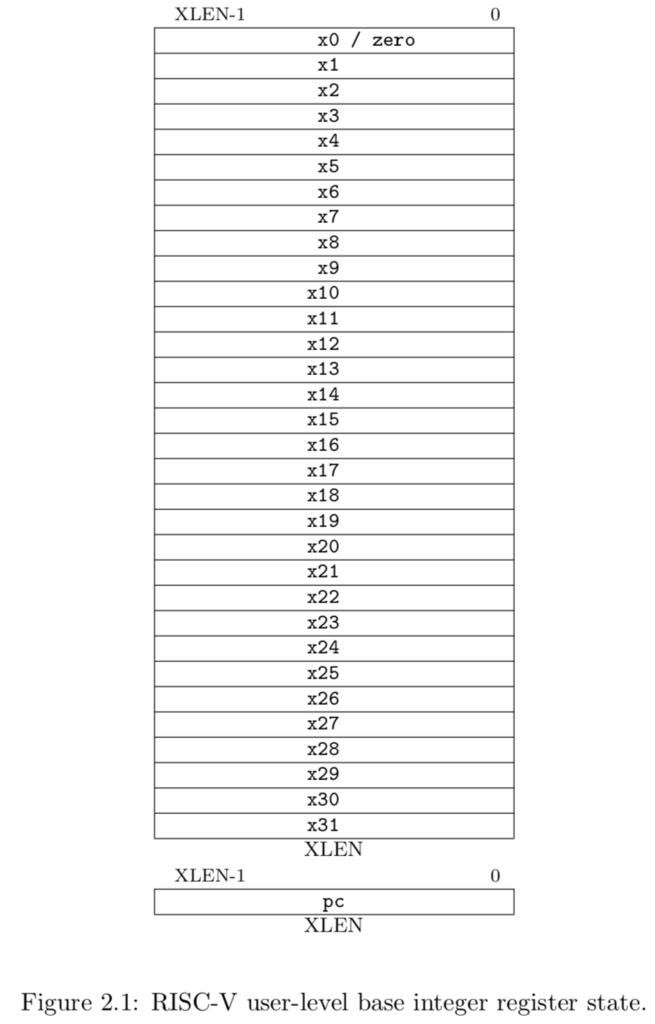

レジスタファイルの構成

- レジスタ長は32/64/128の3タイプ

- レジスタ名は"x + 0〜32"で表す

- x0はゼロレジスタ(値は常に0)